这里写目录标题

- 1、配置文件

- 2、延时信息计算与反标

- 3、时序分析条件

- 4、情形分析

- 5、时序例外

- 6、工作条件

STA静态时序分析,推荐邸老师的B站课程,链接:链接: link

STA基本概述和其中一些内容在之前邸老师笔记中已经涉及了,链接: link

本文介绍一些其他的内容。即STA的批处理命令。

PT的命令行接口执行脚本文件的批处理命令:

pt_shell> pt_shell -file batchmode_analysis.tcl |tee batchmode_analysis.log

1、配置文件

与DC类似,PT启动时也需要一个配置文件来初始化工具的运行环境。该配置文件是采用TCL格式的隐藏文件,文件名为“.synopsys_pt.setup”。PT依次在当前目录、用户主目录、和PT安装目录($PT_PATH/admin/setup)中寻找此文件。主要内容包括:

set search_path [list /home/library/]

set link_path [list {*} smic13_ss.db smic13_ff.db

smic13 IO_ff.db smic13IO_ss.db]

变量search_path 定义了一个列表,它包含了查找库和设计时需查看的自录,免除了当引用库和设计时需要键入完整文件路径的麻烦。

变量link_path 定义了一个库列表,它包含用于设计链接的单元,这些库在search_path 指定的目录中套找。上例中link_path变量定义的列表中有三类元素。“*”表示内存中所加载的设计,另两类分别是表示最差工作情况和最好工作情况的标淮单元工艺库和 PAD 库。

对于同名的环境变量,后装载的配置文件将覆盖先装载的配置文件。由于用户不同设计采用的工艺可能不同,建议工作日录下保存配置文件。

如果不想使用“synopsys_pt.setup”文件,另一个广泛使用的设置环境的方法将配置信息以TCL格式写入文件,如smicl8.env,然后在pt_shell中使用 source命令。

pt_shell> source smic18.env

2、延时信息计算与反标

PT沿着每条时序路径进行延时计算。一条路径的总延时为该路径上所有单元延时和连线延时之和。延时计算方法取决于芯片版图是否完成。物理设计完成之前,芯片拓扑未知,故PT采用线负载模型估计连线延时;物理设计完成后,其他工具可以精确确定连线延时并写入标准延时格式 (Standard Delay Format,SDF)文件。PT读入SDF 文件进行精确的时序分析。

布局布线工具可以提供详细和精确的延时信息,PT基于此类信息进行精确的时序分析,这一过程称为延时反标 (delay back-annotation)。反标的信息通常以SDF形式提供。PT支持SDF的1.0至2.1 版本以及3.0的子集,使用read_sdf命令读入 SDF 包含的延时信息。read_sdf命令有多个参数,可参阅 Prime Time user guide 或在 PT 的命令行中用 man 命令查看。

PT也可以根据连线寄生电容和电阻的详细描述进行精确的延时计算。PT支持集总电容 (lumped capacitance)、集总电阻 (humped resistanee)、所见Π模型(reduced pi model)以及详细RC网络 (detailed RC network)等格式的电路延时信息。缩减Π模型以及详细RC 网络形式的延时信息比集总电容、集总电阻的延时信息精确,但需要消耗更多的 CPU 时间与内存。奇生参数格式包括缩减标淮寄生参数格式(Reduced Standard Parasitic Format, RSPF)、标准寄生参数交换格式(Standard Parasitic Exchange Format, SPEF)以及详细标准寄生参数格式 (Detailed Standard Parasitic Format, DSPF)。

3、时序分析条件

PT根据用户指定的条件进行时序分析,这些条件包括输入延时、输出延时、端口电容、线负载模型和工作条件等,对应概念与逻辑综合DC类似,此处不再赘述。

4、情形分析

情形分析 (case analysis)指进行时序分析时,可以使用逻辑常量或端口/引脚上的逻辑翻转来限制信号在设计中的传播。需要注意的是:1)情形分析只将信号常量从指定位置处前向传播;2)默认情况下,禁止常量传播通过时序单元,如要使能,需要设置变量:case_anasysis_seqzential_propagation为 always。

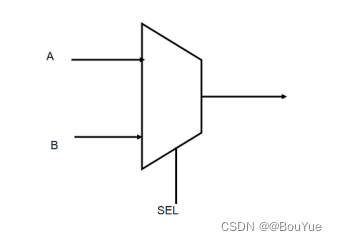

设为 0,该值禁止信号B传播通过多路选择器到达乙。对应的命令为:

pt_shell>set_case analysis 0 select

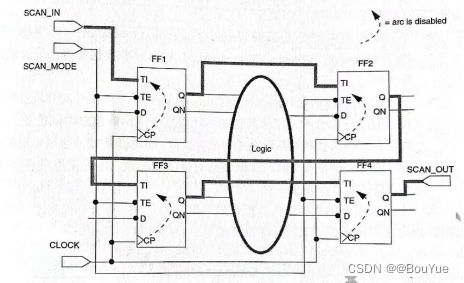

情形分析最常用的情况是禁止扫描链,如下图所示。设置SCAN_MODE为0可以禁止扫描链,这样,report_timing命令就不会报告扫描链的信息。对应的命令为:

pt_shell>set_case_analysis 0 [get_ports "SCAN_MODE"]

如果要删除情形分析的值,需要用到 remove_case_analysis命令。如要删除设计test_port的情形分析,使用命令:

pt_shell>remove_case_analysis test_port

情形分析可以使用一个命令完成在正常模式或测试模式下整个设计的时序分析。但如果只想禁止某条时序路径,则可以采用 set_disable_timning命令。

5、时序例外

默认情况下,PT假设路径起点发射的数据是下一个时钟沿在路径终点被捕获。而对于工作方式并非如此的路径,需要指定时序例外进行区分,否则,时序分析的结果将与实际电路的行为不匹配。

指定时序例外,可以:

设置虚假路径。即指定设计存在的某条逻辑路径不被工具进行时序分析,采用set_false_path命令。设置虚假路径将删除该路径上的时序约束。

设置路径最大延时和最小延时。即使用指定的最大延时值和最小延时值来覆盖路径上默认的建立时间约束和保持时间约束,采用set_max_delay和set_min_delay命令。

设置多周期路径。即指定从路径的起点到终点传输数据所需要的时钟周期数,采用set_multicycle_path命令。

6、工作条件

半导体器件的参数会随着制造工艺、工作温度和电源电压的变化而变化。PT使用命令set_operating_conditions 来指定分析时的工作条件。PT支持的时序分析方法包括:

单一工作条件模式 (single operating condition mode)。即根据一组PVT (Process、 Voltage、 Temperature)的延时参数进行整个设计的时序分析。

片上参数变化模式 (On-chip variation mode)。即在一次分析过程中对不同路径综合考虑工作条件的两种极端情況。对建立时间检查,PT对发射时钟路径和数据路径采用最大延时,而对捕获时钟路径采用最小延时;对保持时间检查,PT对发射时钟路径和数据路径采用最小延时,而对捕获时钟路径采用最大延时。

最后

以上就是坚强仙人掌最近收集整理的关于EDA15--STA静态时序分析--批处理命令(一)1、配置文件2、延时信息计算与反标3、时序分析条件4、情形分析5、时序例外6、工作条件的全部内容,更多相关EDA15--STA静态时序分析--批处理命令(一)1、配置文件2、延时信息计算与反标3、时序分析条件4、情形分析5、时序例外6、工作条件内容请搜索靠谱客的其他文章。

发表评论 取消回复