System Timer (STM)

The STM is designed for global system timing applications requiring both high precision and long period.

Feature List

The STM has the following features:

• Free-running 64-bit counter

• All 64 bits can be read synchronously

• Different 32-bit portions of the 64-bit counter can be read synchronously

• Flexible service request generation based on compare match with partial STM content(主要是通过比较寄存器产生2路中断)

• Counting starts automatically after an Application Reset

• STM registers are reset by an Application Reset if bit ARSTDIS.STMxDIS is cleared. If bit ARSTDIS.STMxDIS is set, the STM registers are not reset by application reset, and are reset by system reset instead.

Special STM register semantics provide synchronous views of the entire 64-bit counter, or 32-bit subsets at different levels of resolution.

Functional Description

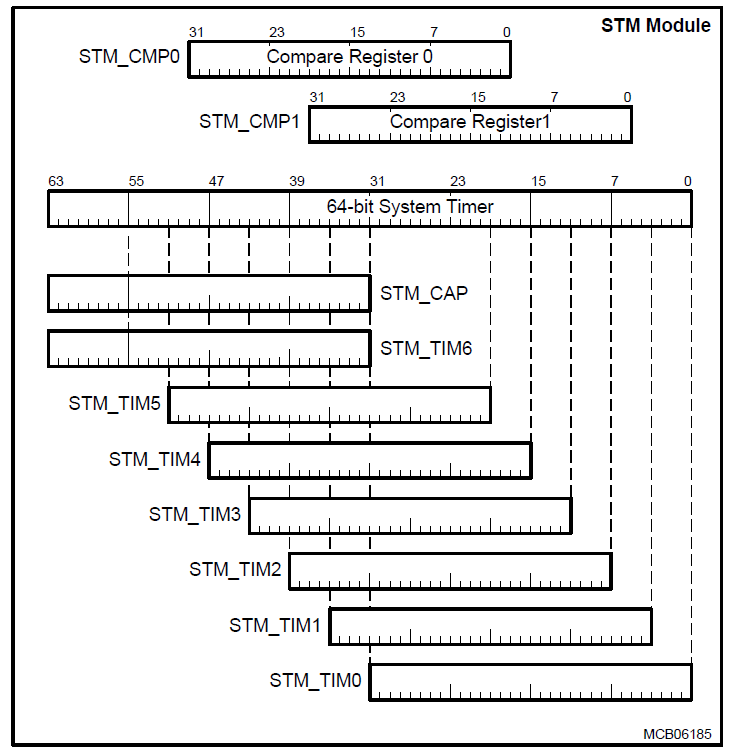

32位寄存器STM_TIM0至STM_TIM6以此分段读取64位系统定时器的值,由于STM系统定时器为64位,单片机位32位,所以不能通过一条指令读取64位定时器的所有值,需要两条指令,为了避免两条指令之间计数器的差别,需要通过寄存器STM_CAP在第一条指令时自动捕捉高32位的值。

32位寄存器STM_TIM0至STM_TIM6以此分段读取64位系统定时器的值,由于STM系统定时器为64位,单片机位32位,所以不能通过一条指令读取64位定时器的所有值,需要两条指令,为了避免两条指令之间计数器的差别,需要通过寄存器STM_CAP在第一条指令时自动捕捉高32位的值。

STM_TIMx和STM_CAP都是只读寄存器

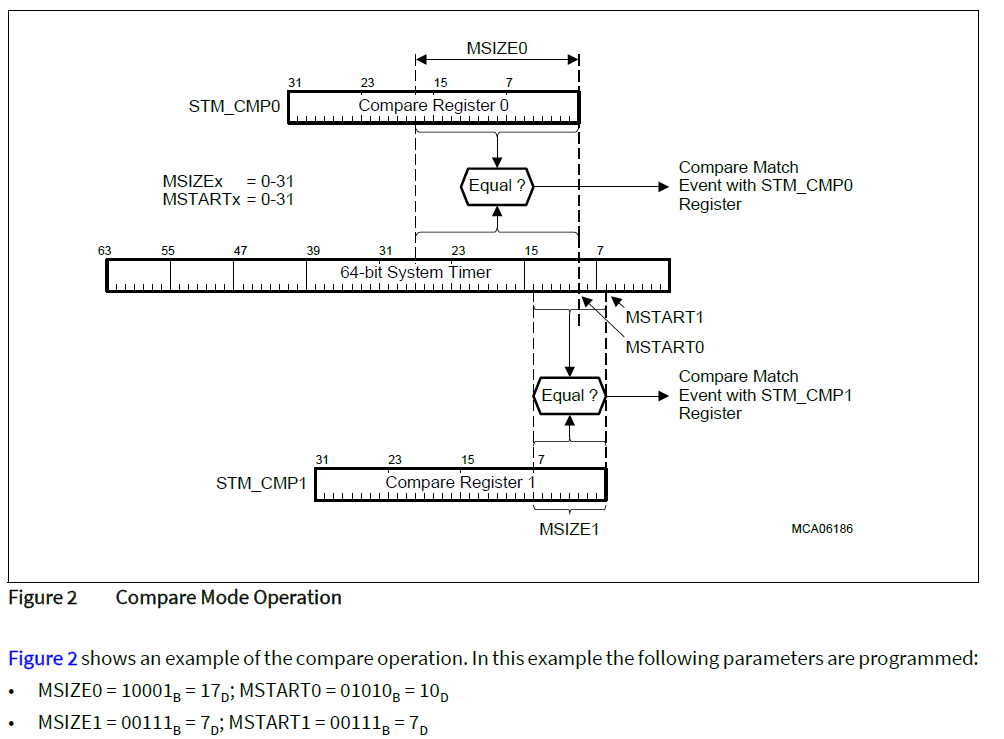

当系统定时器工作时,会自动将系统定时器的值与比较寄存器STM_CMP0和STM_CMP1中设定的值进行比较,相等的时候可以产生中断请求。

Compare Register Operation

两个比较寄存器与系统定时器比较的起始位MSTART和长度MSIZE由寄存器CMCON设定

Compare Match Interrupt Control

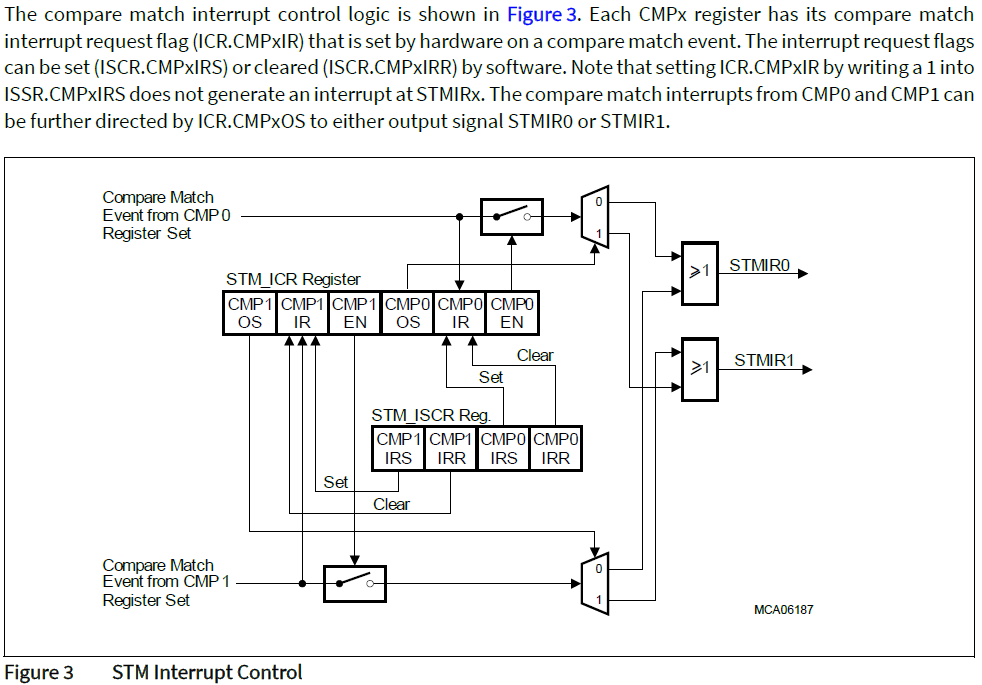

The compare match interrupt flags ICR.CMPxIR are immediately set after an STM reset operation, caused by a compare match event with the reset values of the STM and the compare registers CMPx. This does not directly

generate compare match interrupts because the compare match interrupts are automatically disabled after an STM reset operation (ICR.CMPxEN = 0). Therefore, before enabling a compare match interrupt after an STM

Application Reset, the software should configure the STM and modify the reset values of the compare registers.

Otherwise, undesired compare match interrupt events are triggered. The CMPxIR flags which are set after an STM reset can be cleared by writing register ISCR with CMPxIRR set.

STM as Reset Trigger

A compare match triggered by an CMP0 event can generate a reset in the system. The reset has to be enabled for each STM module individually in register SCU_RSTCON.

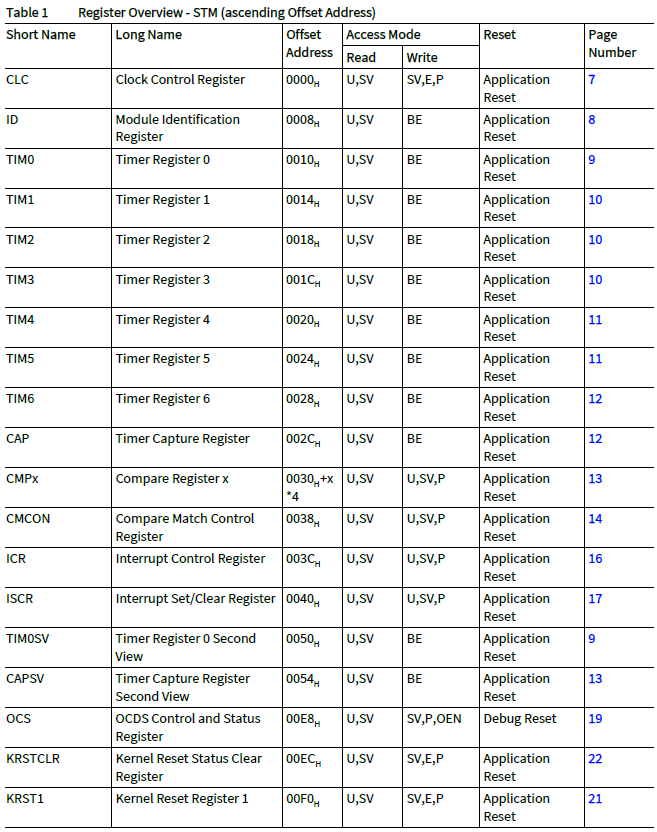

Registers

最后

以上就是不安苗条最近收集整理的关于STM(System Timer)System Timer (STM)的全部内容,更多相关STM(System内容请搜索靠谱客的其他文章。

发表评论 取消回复