文章目录

- 实验准备

- 一、D触发器的门电路实现和仿真

- 1.创建工程

- 2.新建波形文件

- 3.创建 VWF 文件

- 4.波形仿真

- 二、调用D触发器并仿真

- 新建工程

- 创建原理图文件

- 创建 VWF 文件

- 波形仿真

- 三、用Verilog语言实现D触发器并仿真

- 新建工程

- 编写Verilog文件

- 创建 VWF 文件

- 波形仿真

- 参考资料

实验准备

完成安装Quartus 18.1 标准版,软件Modelsim

一、D触发器的门电路实现和仿真

1.创建工程

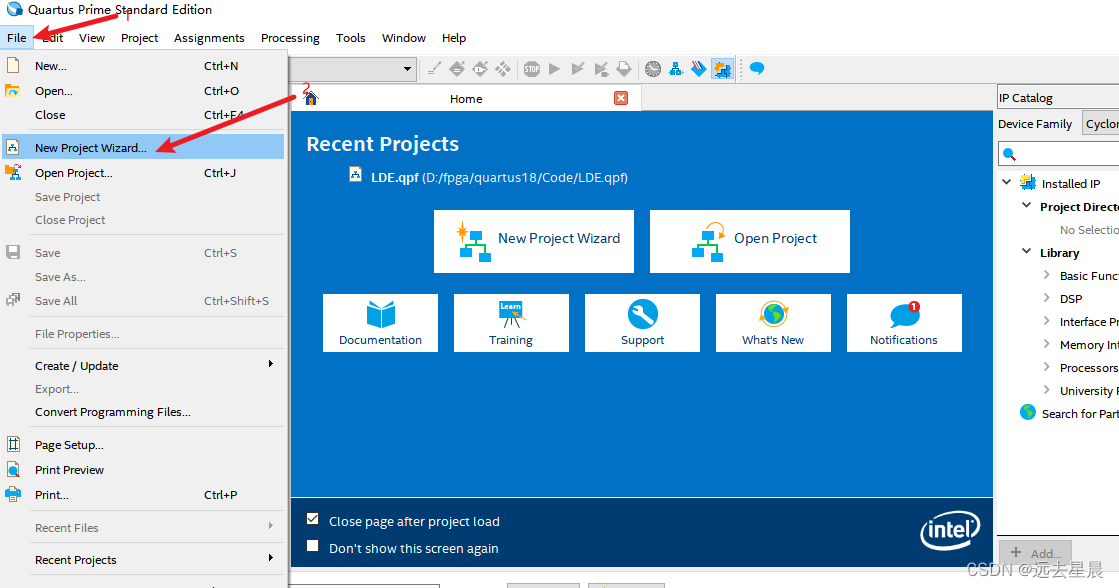

首先点击file->new project wizard,

点击next

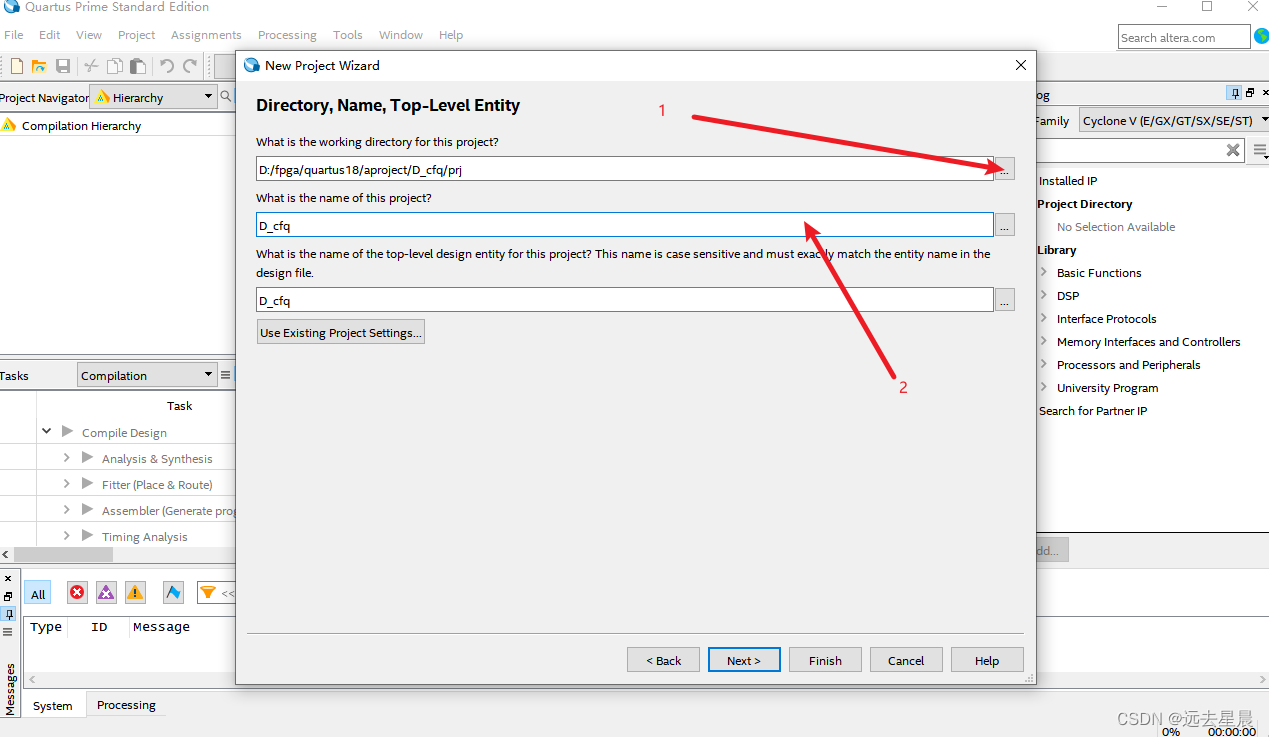

指定工程名字以及顶层文件名

1.选择文件夹新建相关文件夹并确定

2.输入工程名

然后next

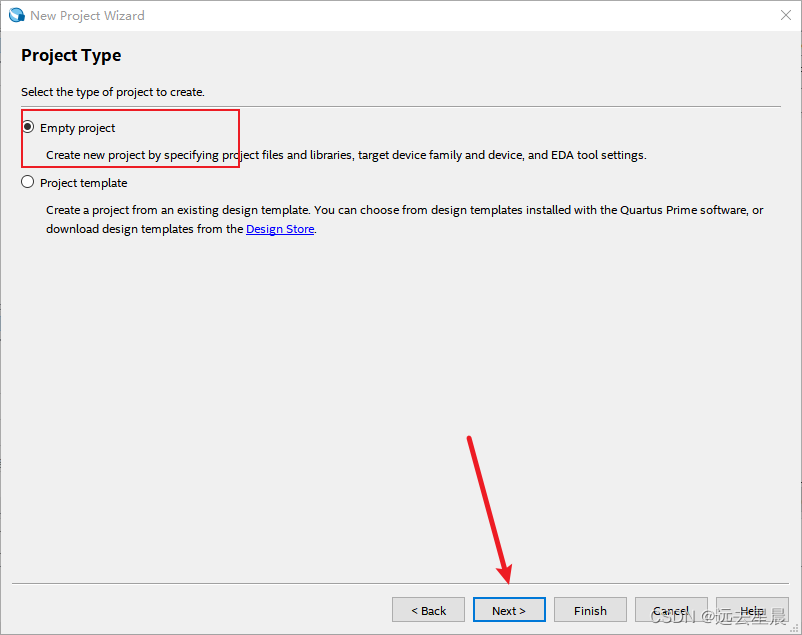

默认,next

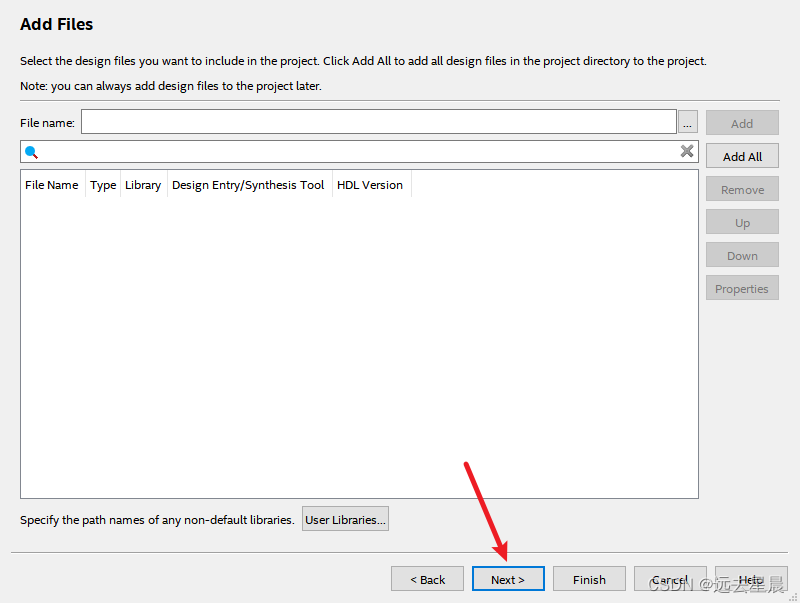

next

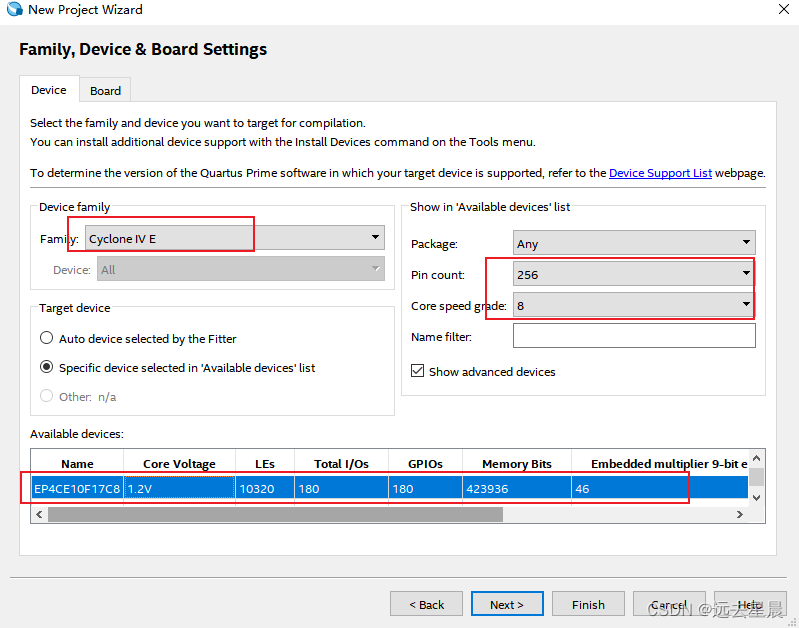

按照该设置找到EP4CE10F17C8,点击 然后next

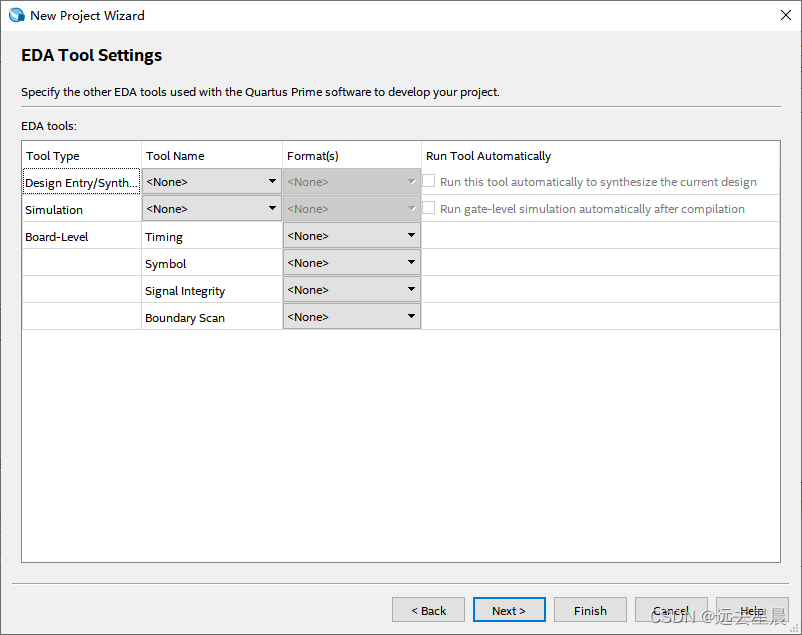

next

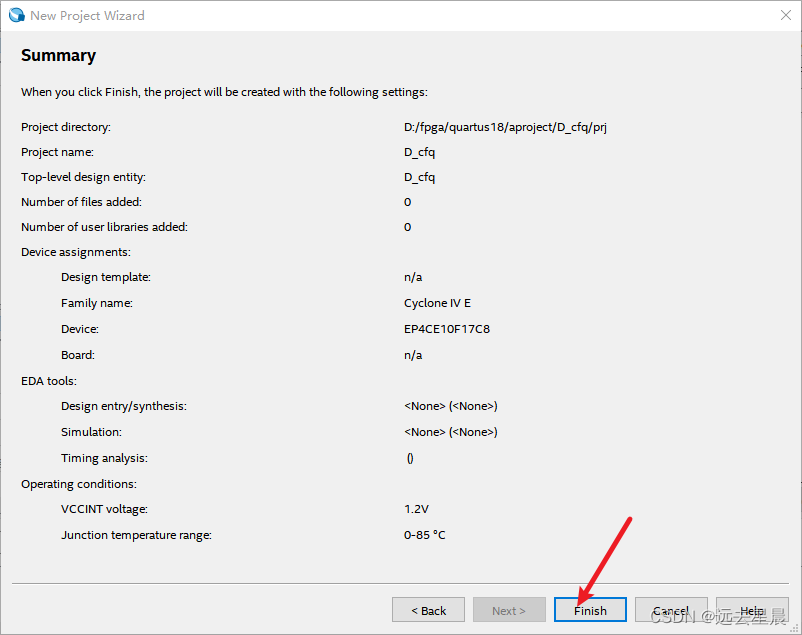

finish完成创建

2.新建波形文件

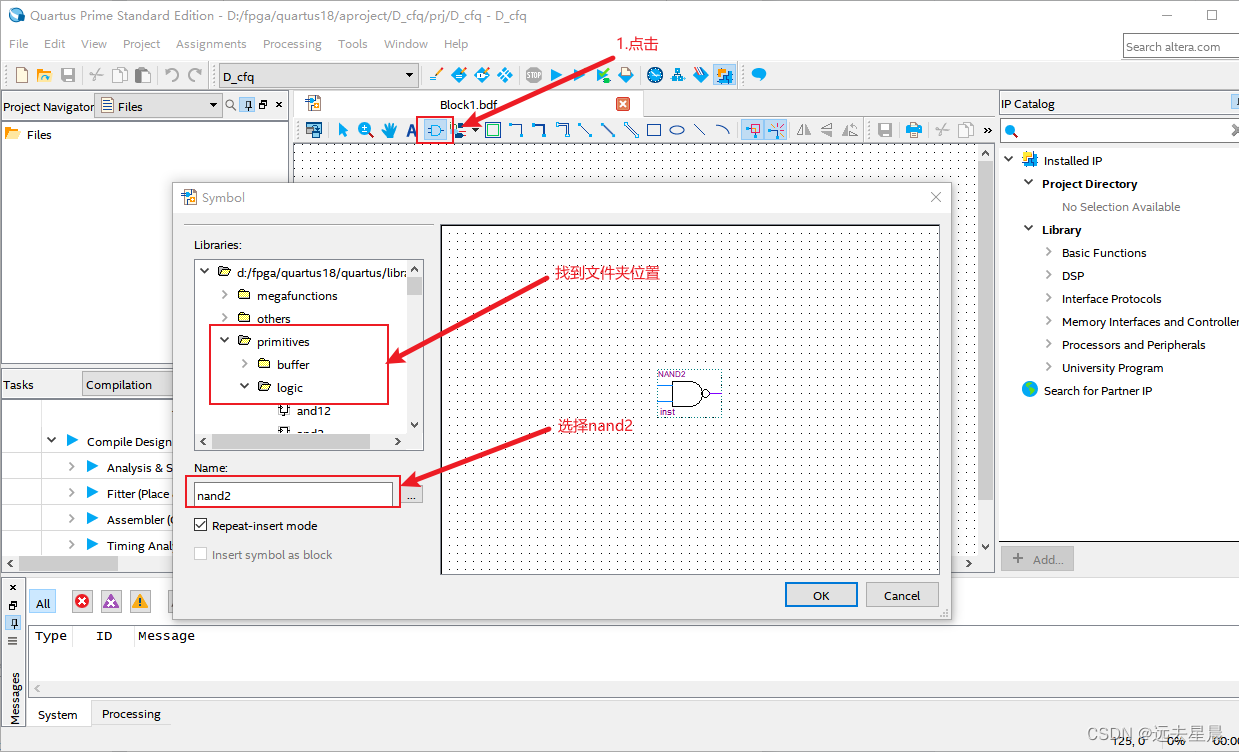

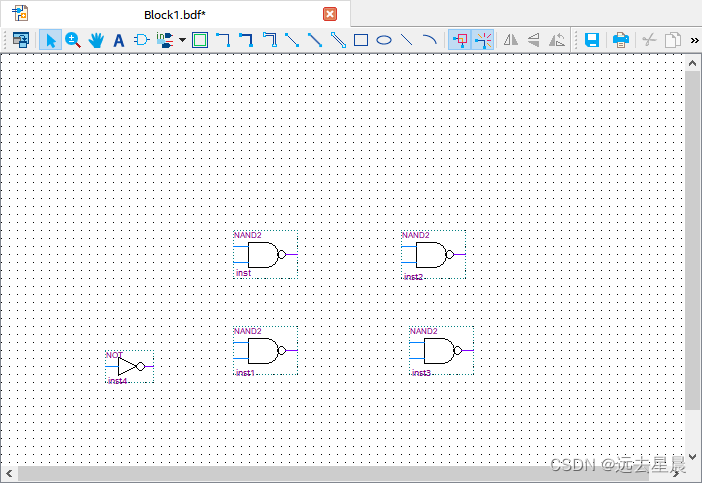

选择nand2,二个输入的与非门,依次添加四个nand2

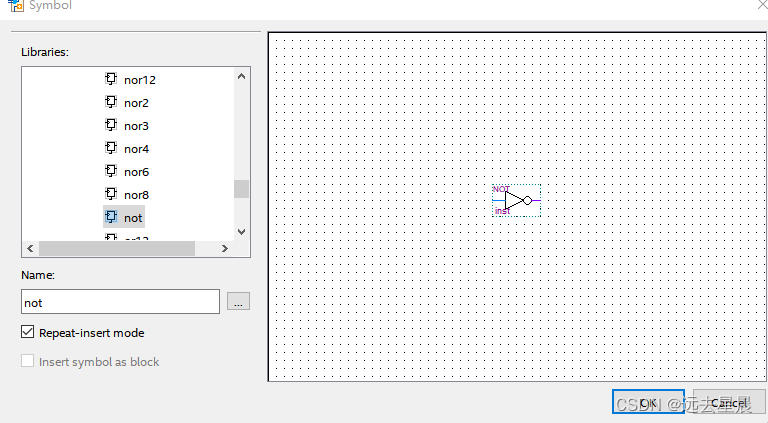

选择非门,添加一个not

结果:

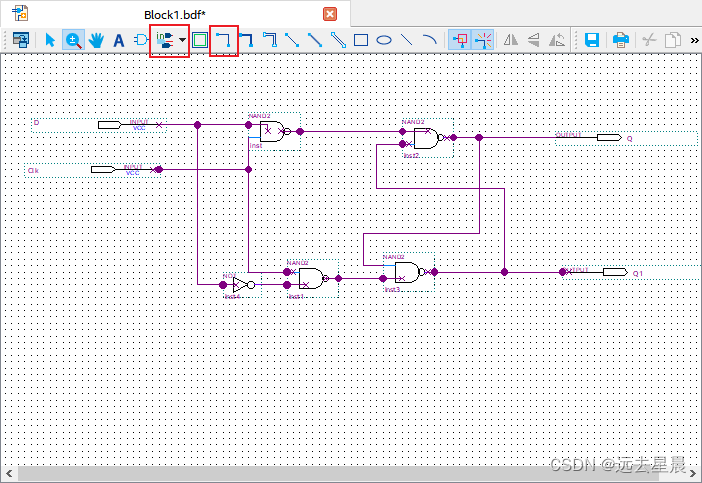

通过工具栏上面输入输出工具,以及连线工具,设计出以下的电路图。

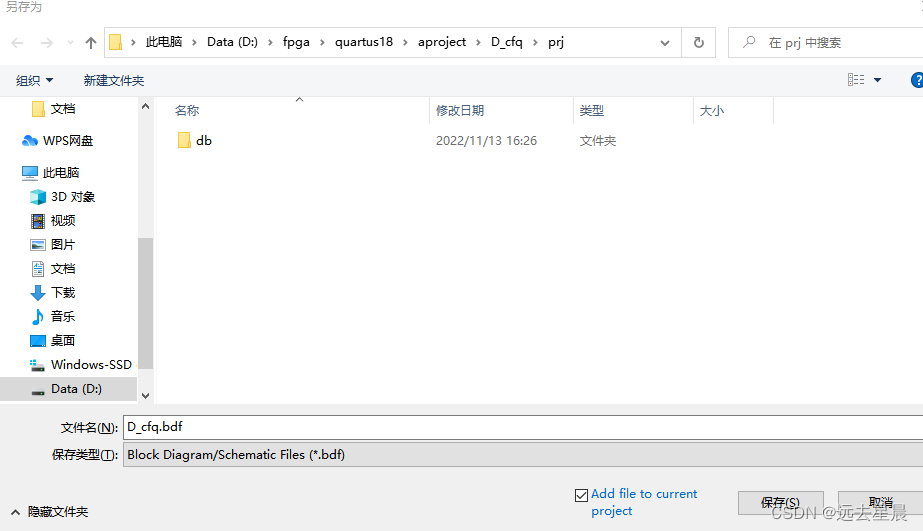

保存

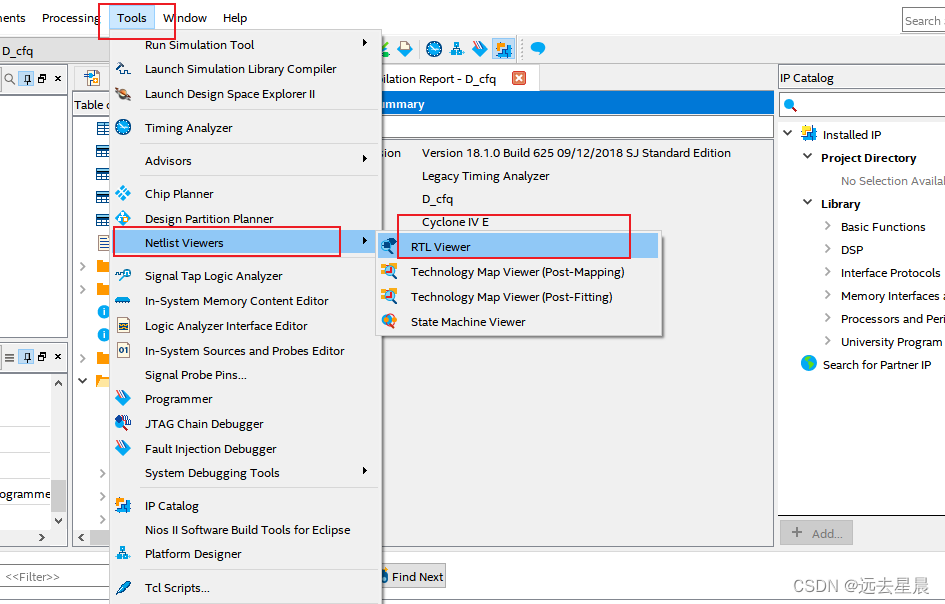

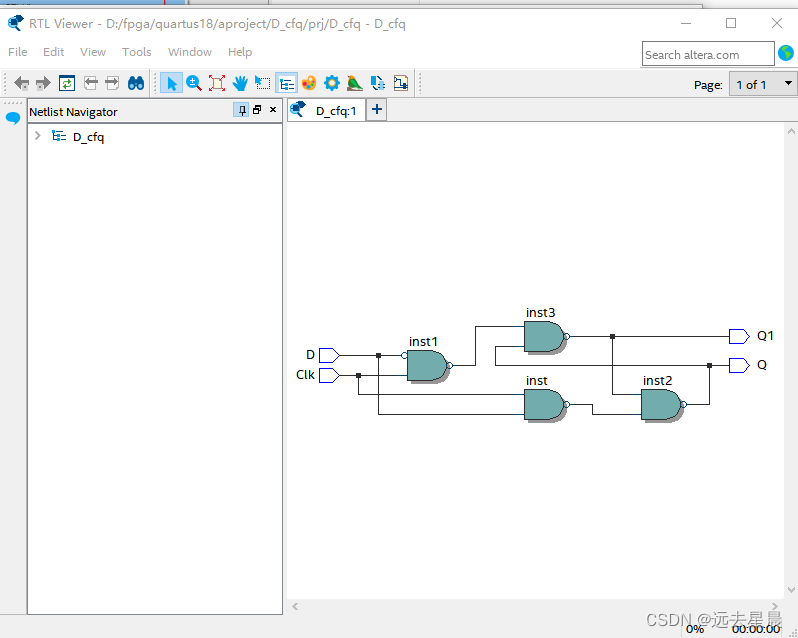

查看硬件电路图

3.创建 VWF 文件

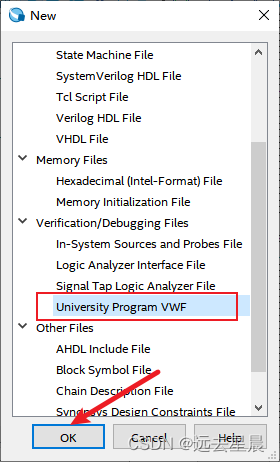

点击【File】→【New】,选择【University Program VWF】。

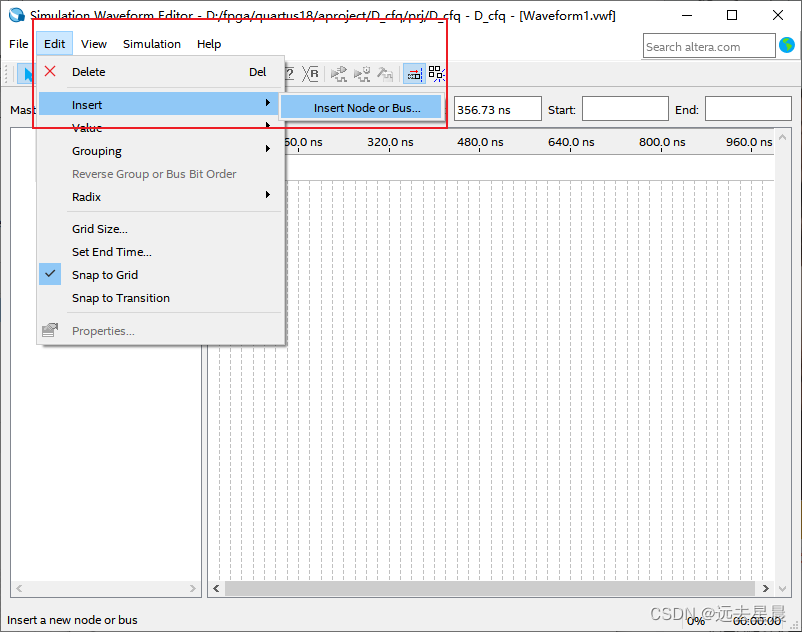

选择【Edit】→【Insert】→【Insert Node or Bus…】。

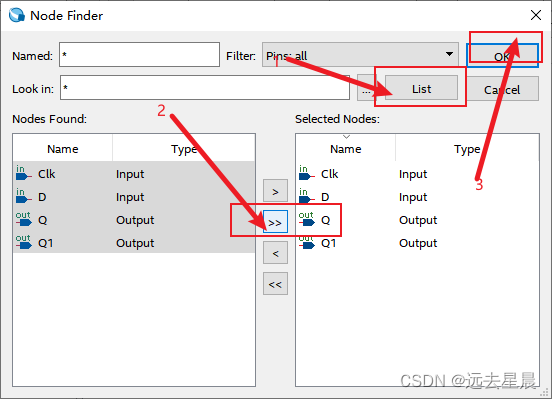

点击【Node Finder…】,然后点击【List】会罗列出四个管脚,点击【>>】选择全部,然后点击【OK】,自动补全了【Name】,然后点击【OK】。

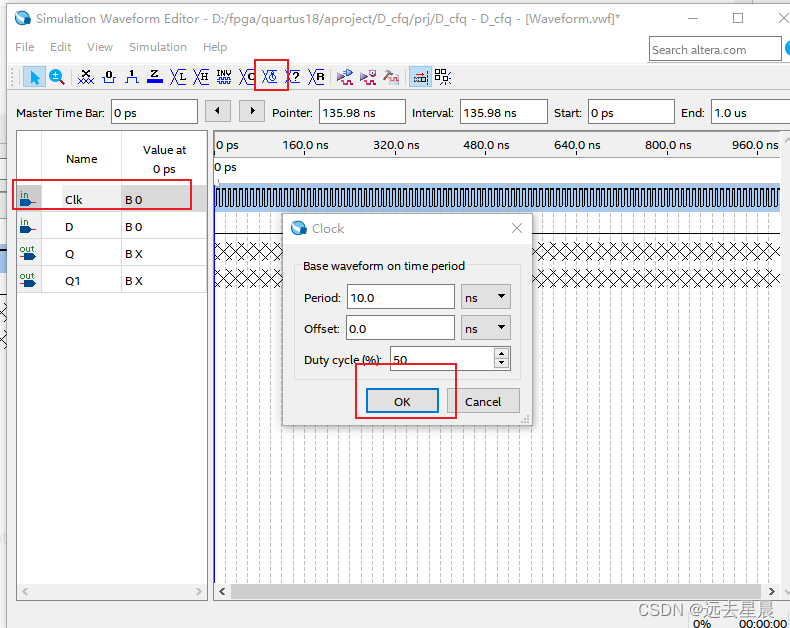

编辑输入 CLK,产生时钟信号。

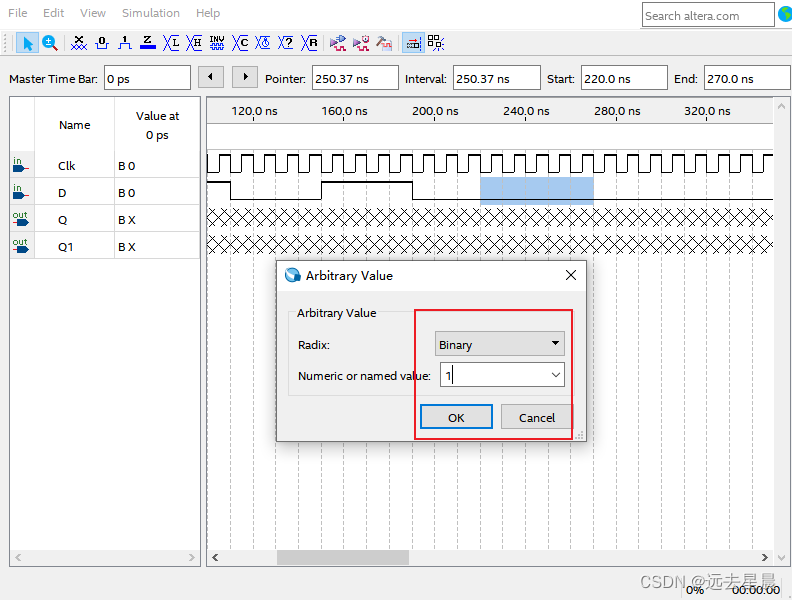

选中要修改的区域,然后双击,修改为 1 ,再点击【OK】即可

保存文件:【File】→【Save】

4.波形仿真

功能仿真:

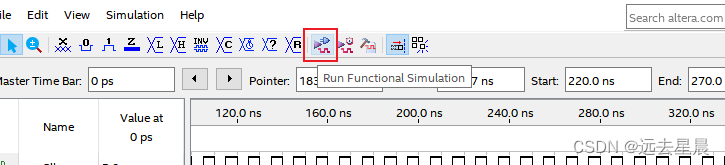

点击【功能仿真按钮——Run Functional Simulation】

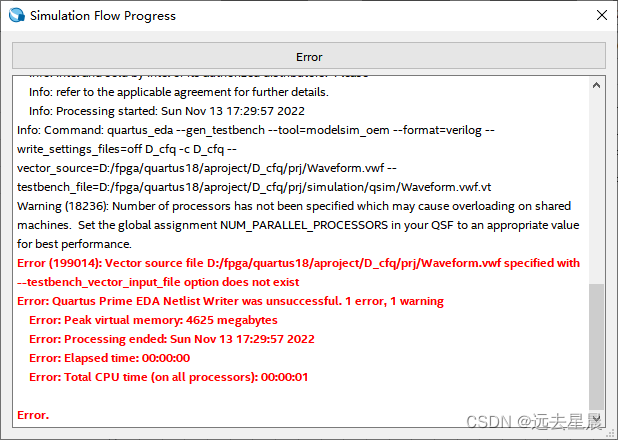

出现错误

解决方法:

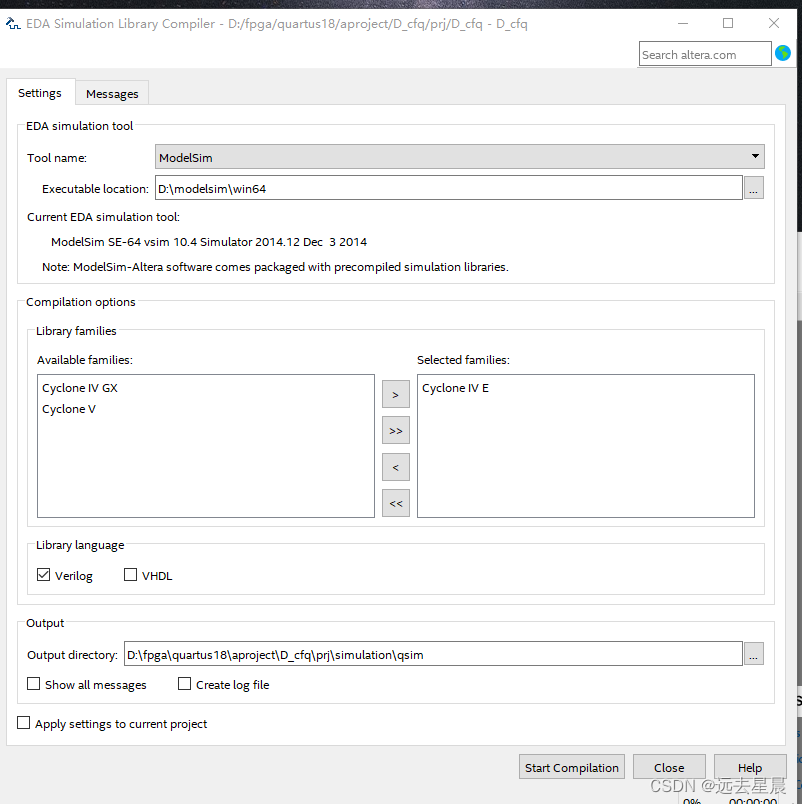

点击【Tools】→【Lauch Simulation Library Compiler】。

选择工程目录下的 …simulationqsim 文件夹,然后点击【Start Compilation】。

点击【Close】关闭窗口。

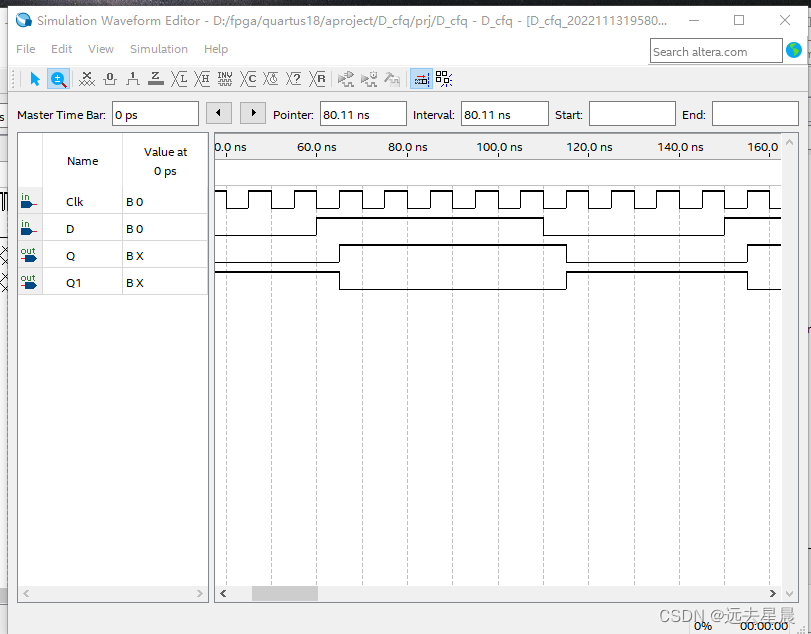

功能仿真:

延迟了半个时钟周期

时序仿真:

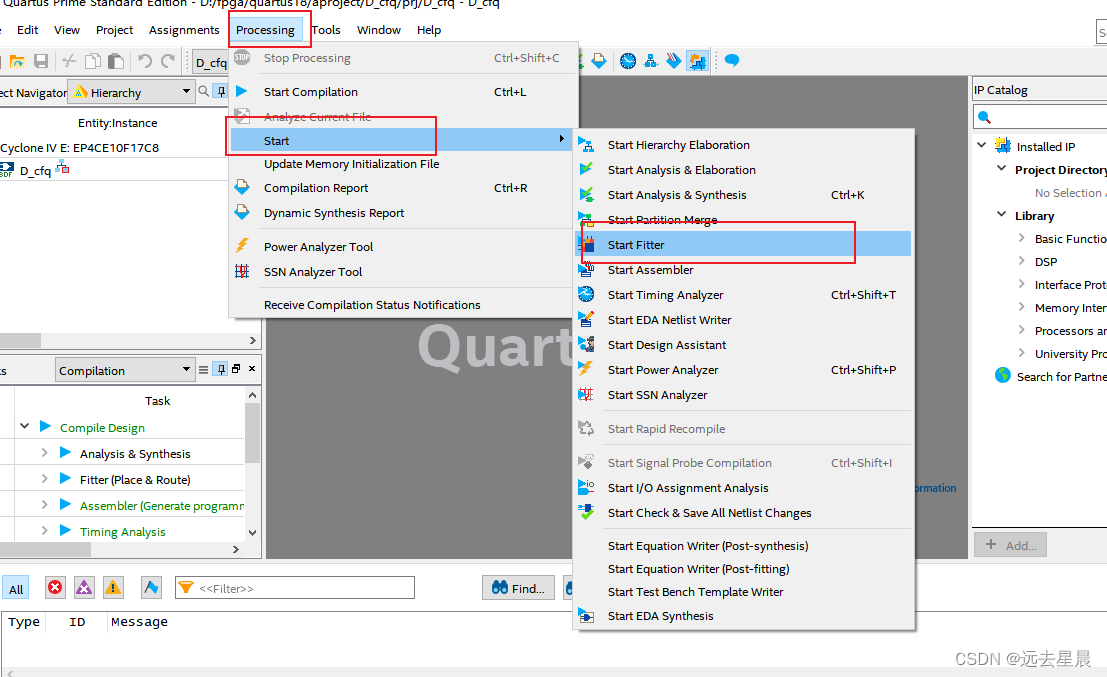

主界面【Processing】→【Start】→【Start Fitter】。

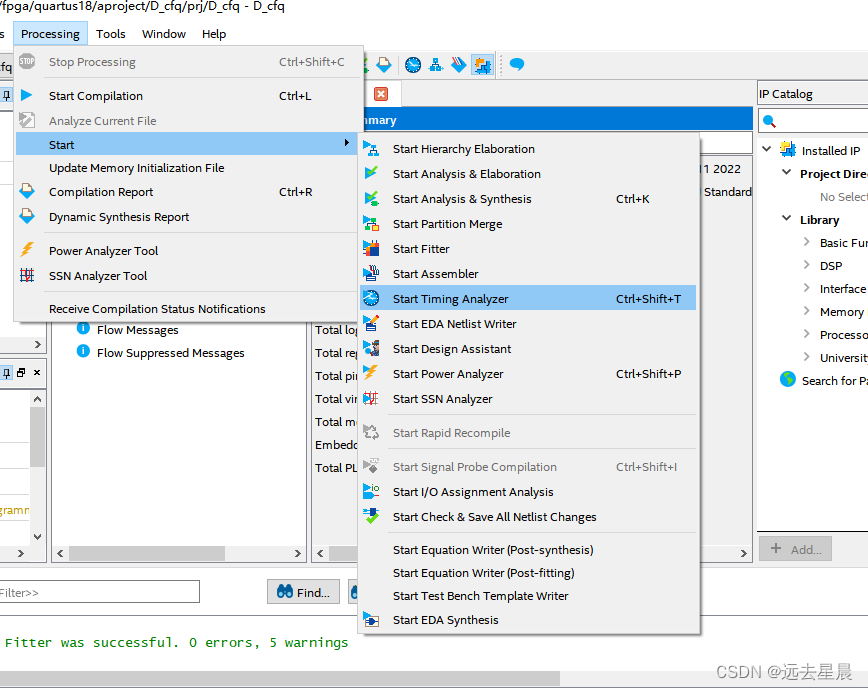

点击【Start TimeQuest Timing Analyzer】。

返回 VMF 文件界面:点击【时序仿真按钮——Run Timing Simulation】。

延时一个周期。

二、调用D触发器并仿真

新建工程

同第二部分一样。

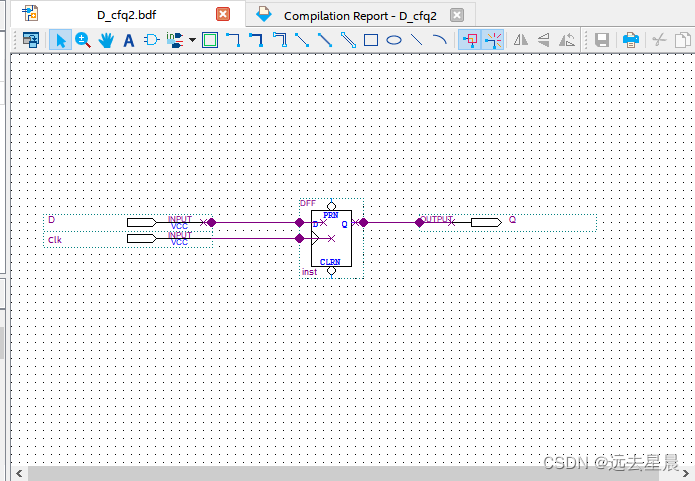

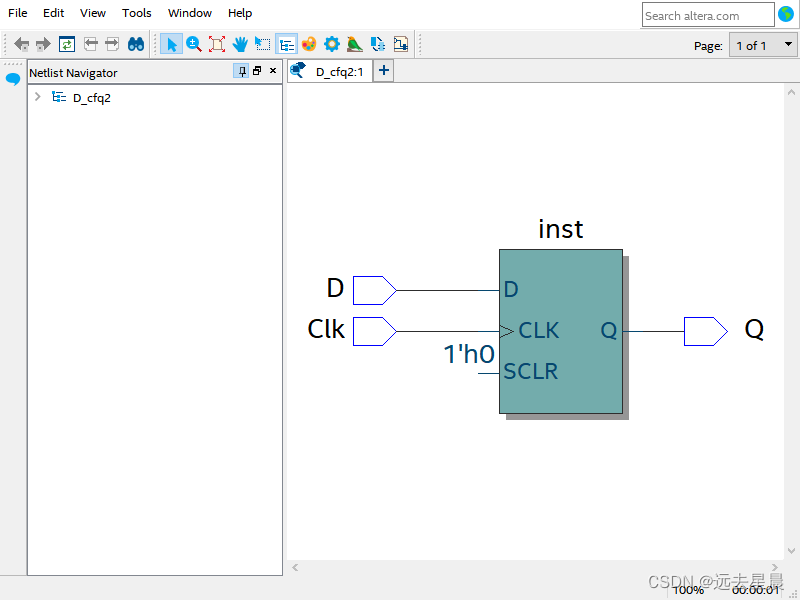

创建原理图文件

同第二部分一样。

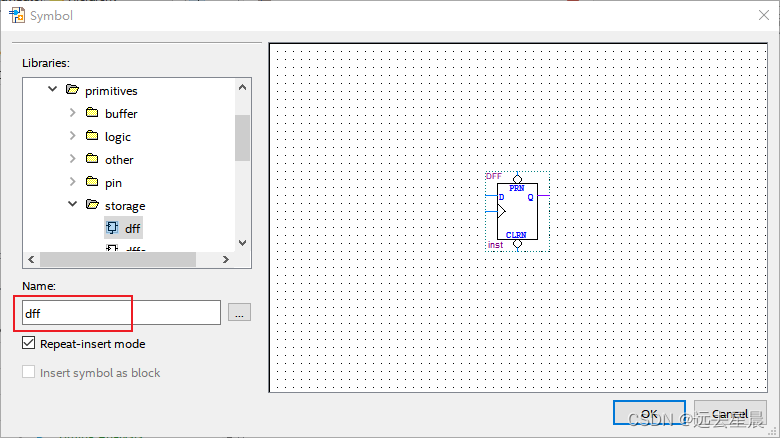

这时,不再画D触发器的内部结构了,而是直接调用D触发器,元件名:dff。

构建如图电路图

编译原理图文件

同第二部分方法一样。

先编译,再查看硬件电路图。

创建 VWF 文件

方法同第二部分一样,

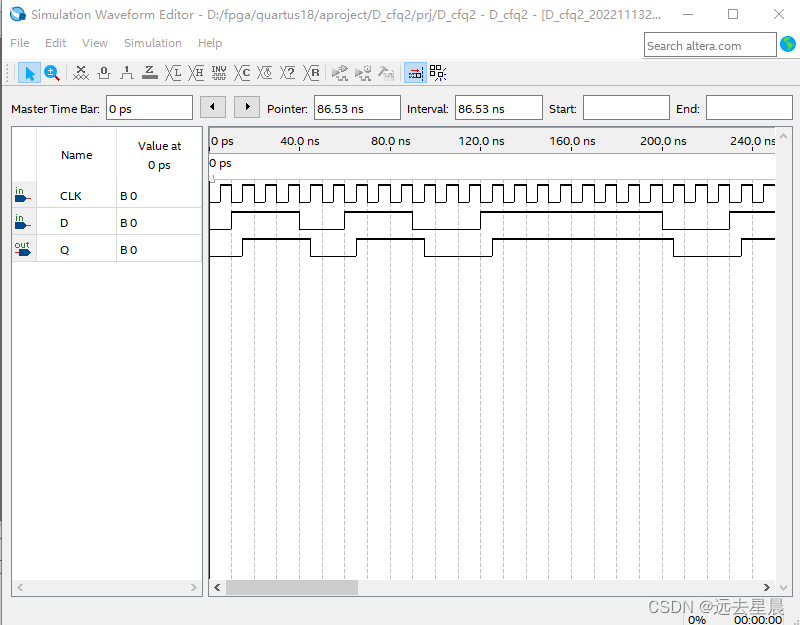

波形仿真

方法同第二部分一样,先编译一下,让它报错,再用解决方法。

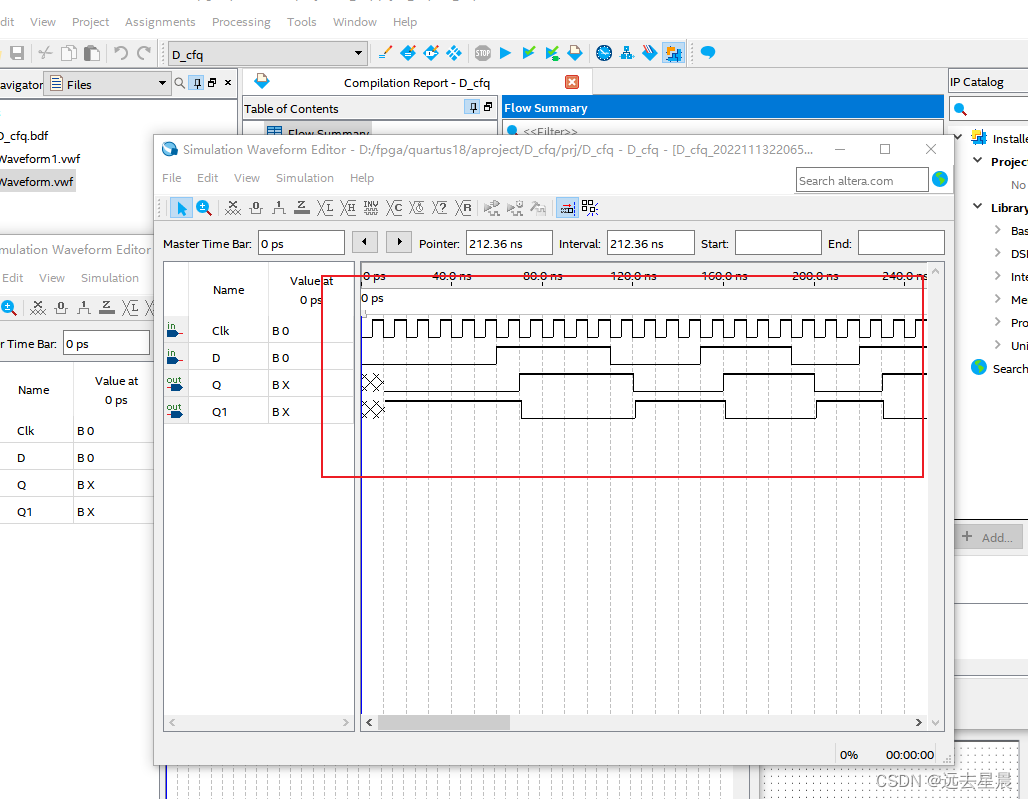

功能仿真(只有半个时钟周期的延迟):

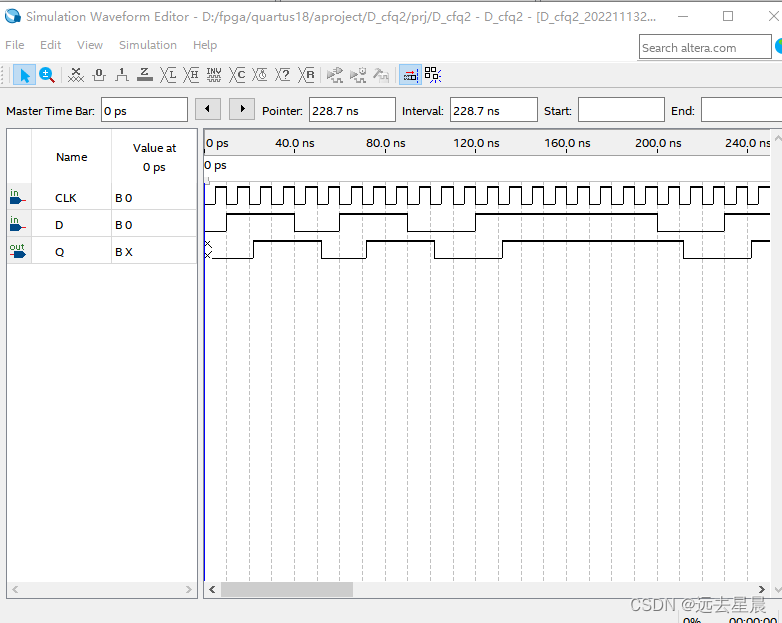

时序仿真

过程同上

延时时间稍微大于一个周期,没第一个标准

三、用Verilog语言实现D触发器并仿真

新建工程

方法同上。

编写Verilog文件

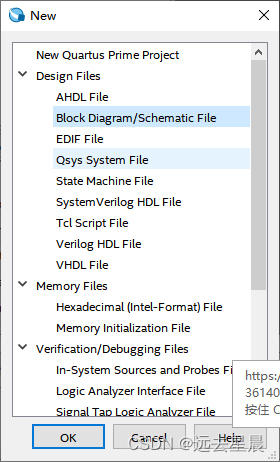

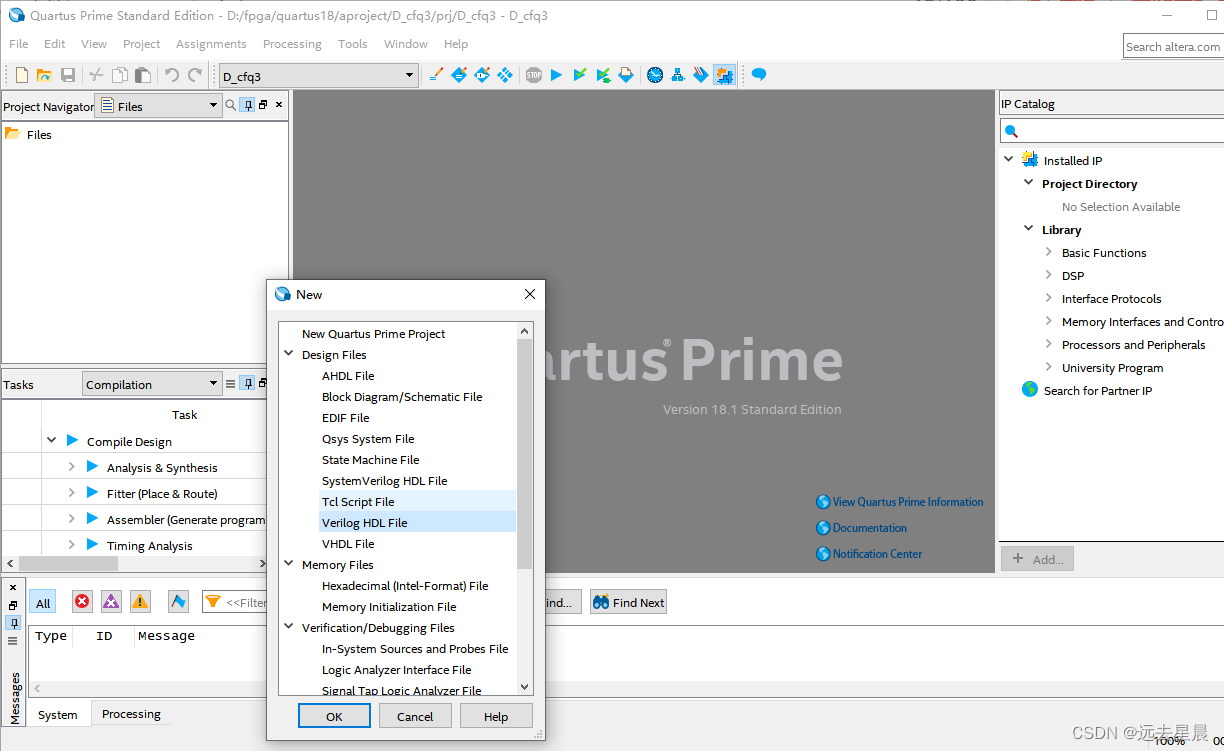

【File】→【New】→【Verilog HDL File】。

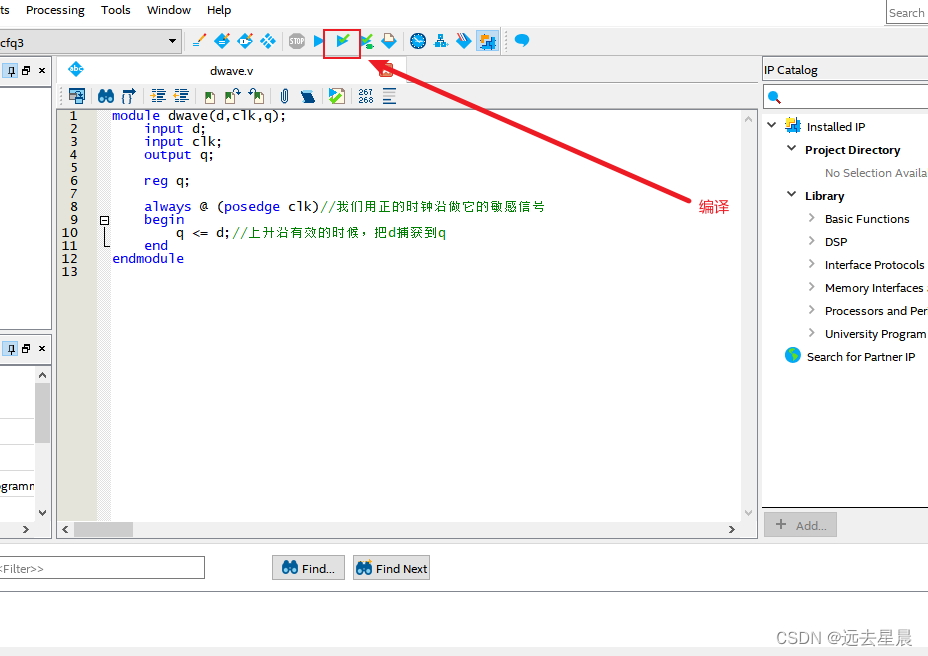

复制粘贴如下代码:

module D_cfq3(d,clk,q);//顶层文件名

input d;

input clk;

output q;

reg q;

always @ (posedge clk)//我们用正的时钟沿做它的敏感信号

begin

q <= d;//上升沿有效的时候,把d捕获到q

end

endmodule

保存编译

创建 VWF 文件

方法同第二部分一样,

波形仿真

方法同第二部分一样,先编译一下,让它报错,再用解决方法。

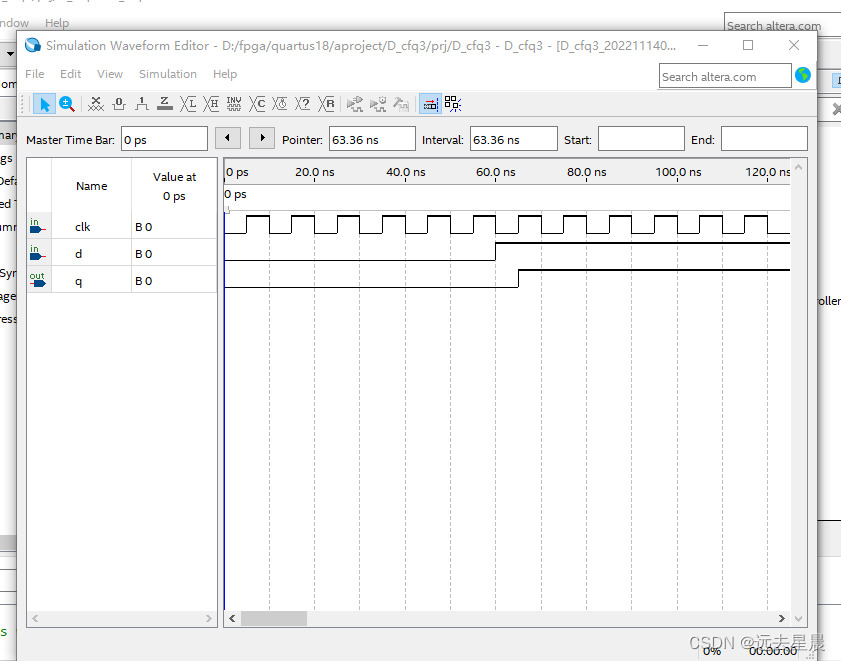

功能仿真(只有半个时钟周期的延迟):

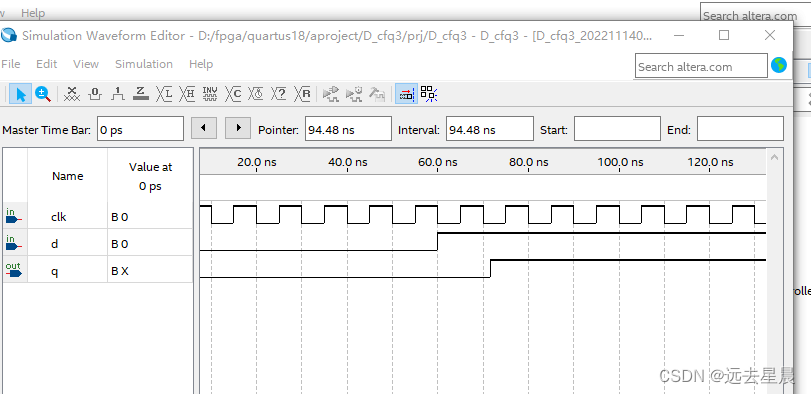

时序仿真

结果与2完全相同,没有1标准

参考资料

https://blog.csdn.net/weixin_46129506/article/details/123443865

最后

以上就是悲凉母鸡最近收集整理的关于使用Quartus 18.1完成D触发器的门电路实现&&直接调用&&Verilog语言实现实验准备一、D触发器的门电路实现和仿真二、调用D触发器并仿真三、用Verilog语言实现D触发器并仿真参考资料的全部内容,更多相关使用Quartus内容请搜索靠谱客的其他文章。

发表评论 取消回复