目录

1、跨时钟域时序

1、慢时钟域到快时钟域

2、快时钟域到慢时钟域

2、多时钟

1、整数倍关系

2、非整数倍关系

3、相移

参考说明

基本知识点是一方面,更重要的是能够详细看懂并分析时序报告的各项内容。

1、跨时钟域时序

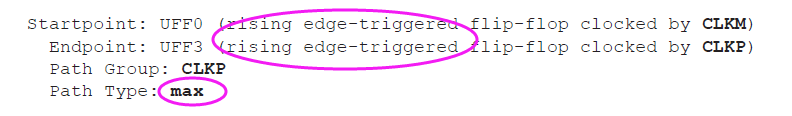

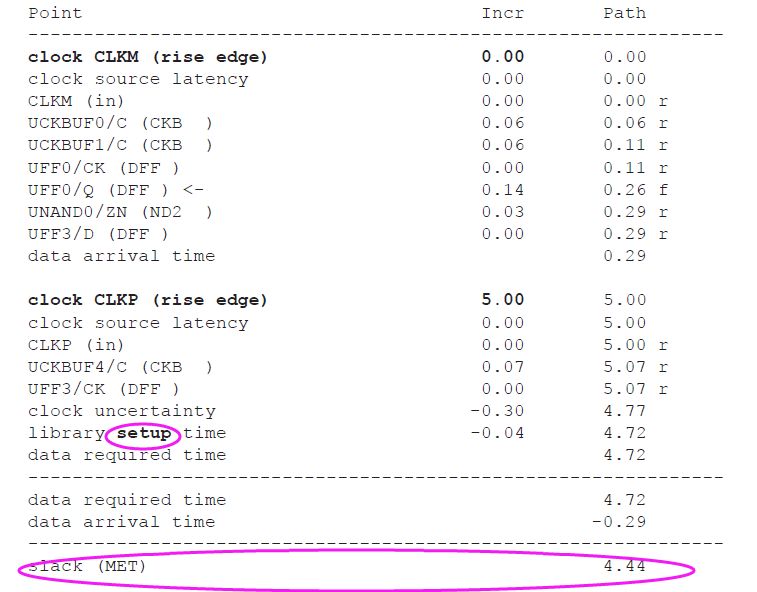

1、慢时钟域到快时钟域

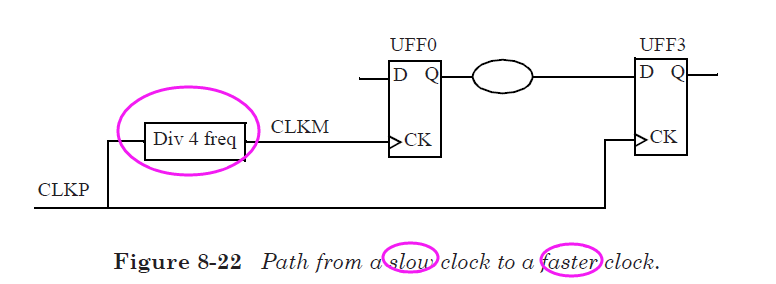

如下图的示例,

需要注意的是,作用在D触发器时钟引脚的两个时钟,都是由CLKP时钟继承而来的,即时钟同源。这种情况可以进行约束。

但是如果两个时钟域完全没有任何关系,即时钟不同源,那么就应该设置伪路径,不让STA进行分析。

#时钟定义:

create_clock -name CLKM

-period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP

-period 5 -waveform {0 2.5} [get_ports CLKP]

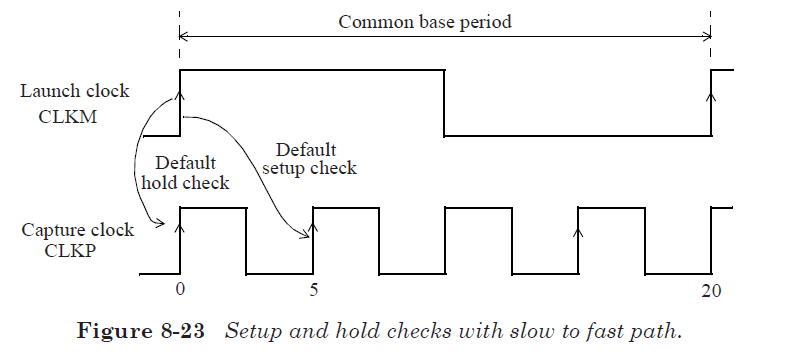

此时的约束一般用多周期约束。如:

set_multicycle_path 4 -setup

-from [get_clocks CLKM] -to [get_clocks CLKP] -end

set_multicycle_path 3 -hold

-from [get_clocks CLKM] -to [get_clocks CLKP] -end2、快时钟域到慢时钟域

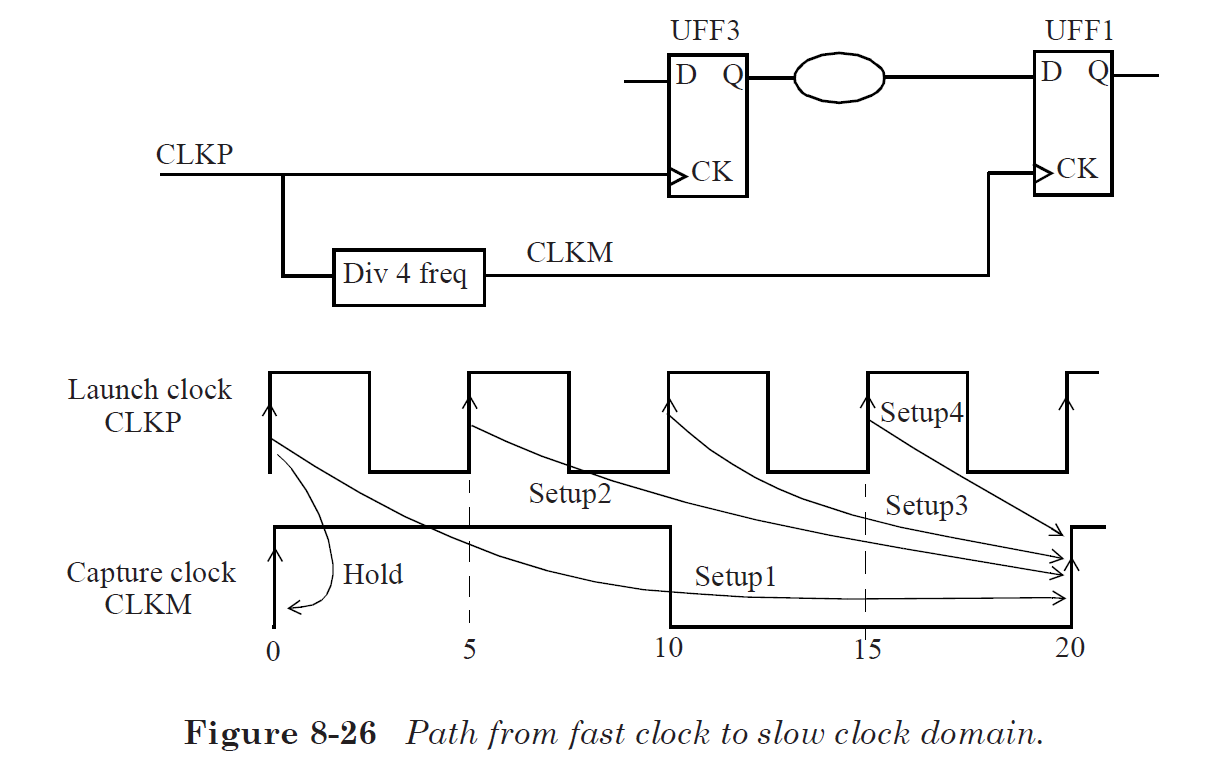

如下图示例,存在4个可能的建立时间。最严格的时序检查是 setup4、0时刻hold

时钟声明:

create_clock -name CLKM

-period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP

-period 5 -waveform {0 2.5} [get_ports CLKP]这种情况下,同样可以用多周期约束:

set_multicycle_path 2 -setup

-from [get_clocks CLKP] -to [get_clocks CLKM] -start

set_multicycle_path 1 -hold

-from [get_clocks CLKP] -to [get_clocks CLKM] -start

# -start 选项 指代发起时钟2、多时钟

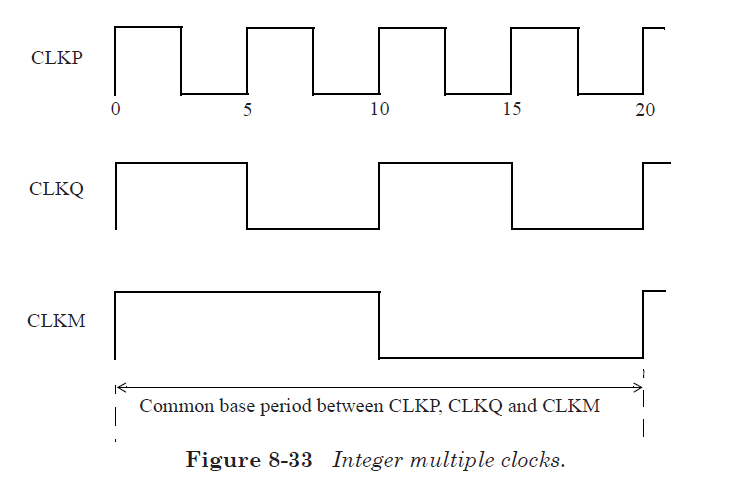

1、整数倍关系

时钟定义:

create_clock -name CLKM

-period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKQ -period 10 -waveform {0 5}

create_clock -name CLKP

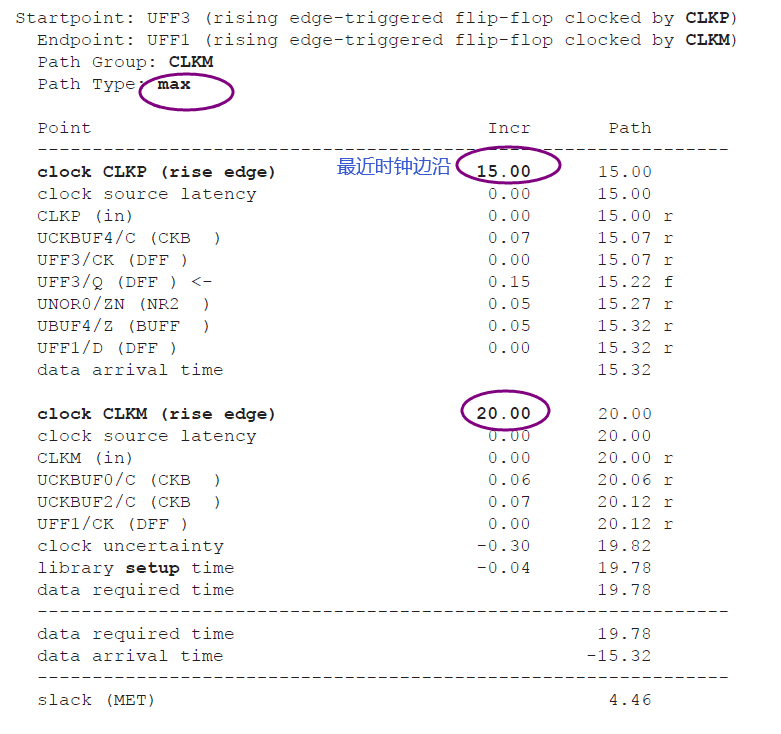

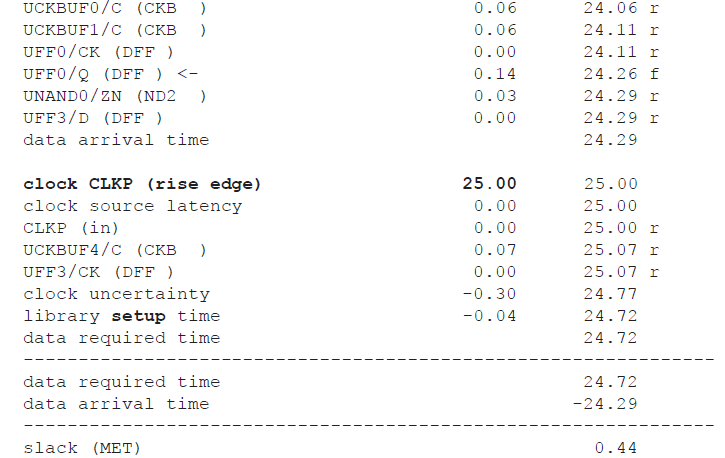

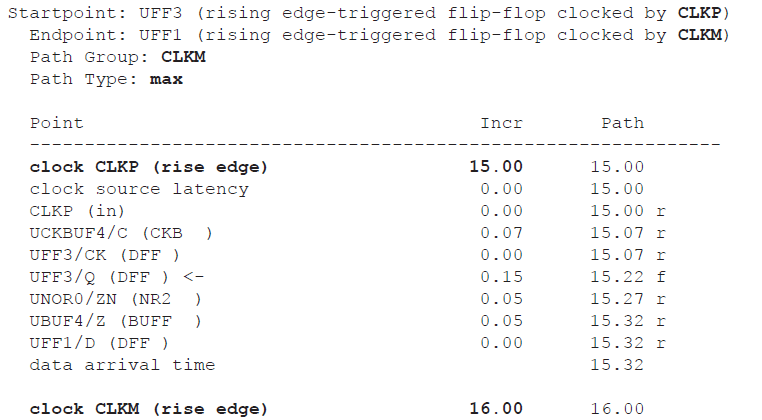

-period 5 -waveform {0 2.5} [get_ports CLKP]建立时序报告:

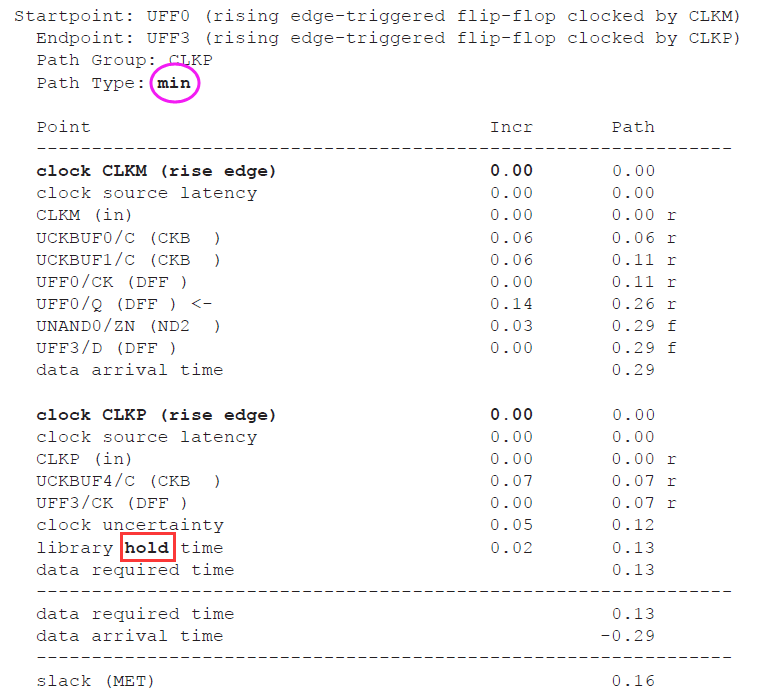

保持时序报告:

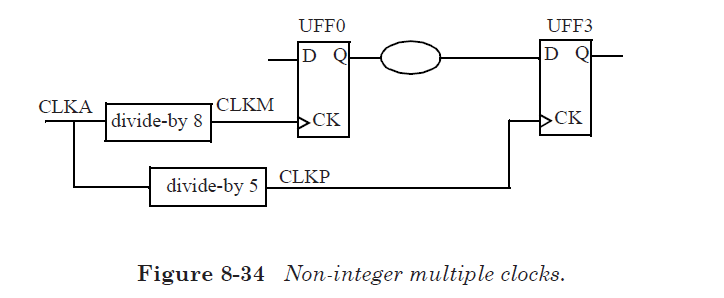

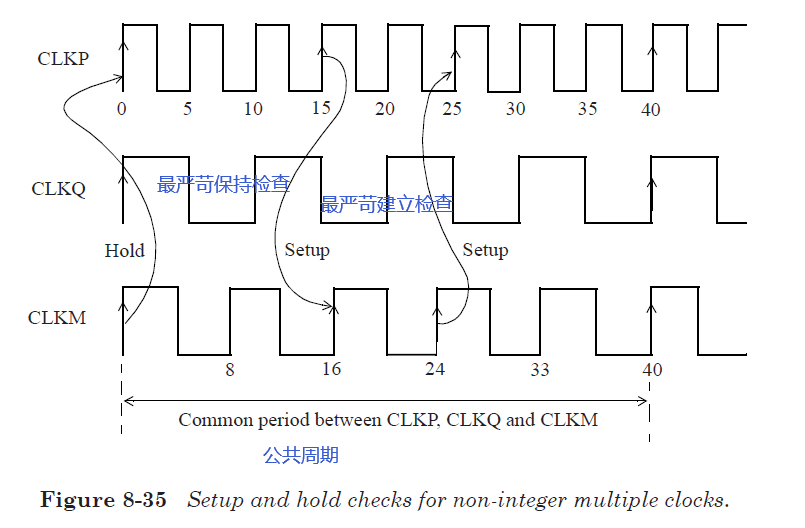

2、非整数倍关系

时钟定义:

create_clock -name CLKM

-period 8 -waveform {0 4} [get_ports CLKM]

create_clock -name CLKQ -period 10 -waveform {0 5}

create_clock -name CLKP

-period 5 -waveform {0 2.5} [get_ports CLKP]

由以上分析:

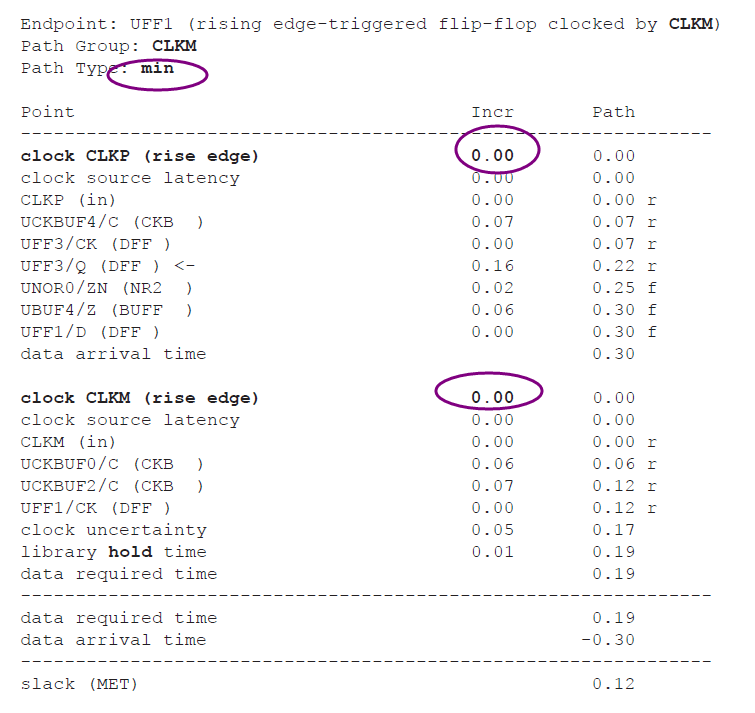

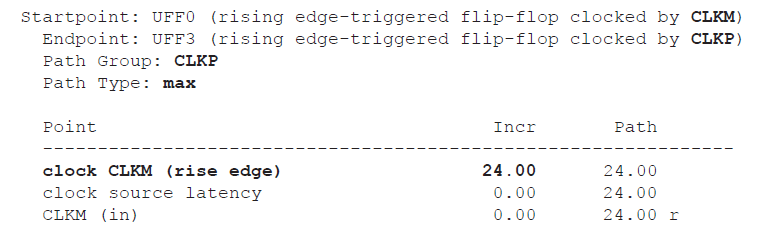

对应的时序报告:

建立检查:

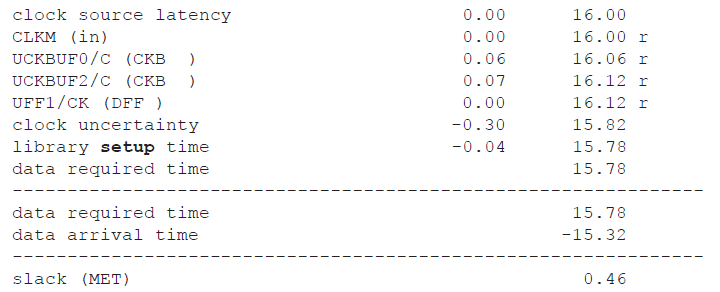

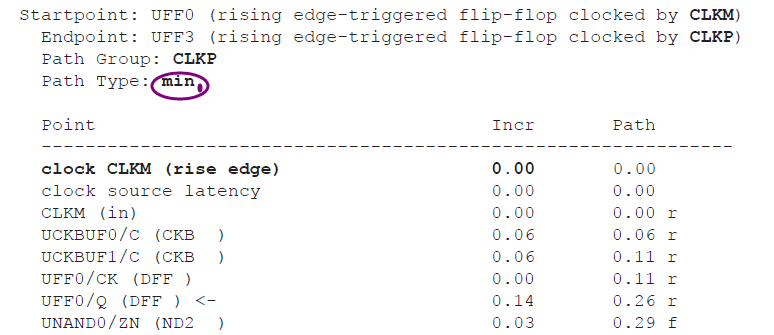

保持检查:

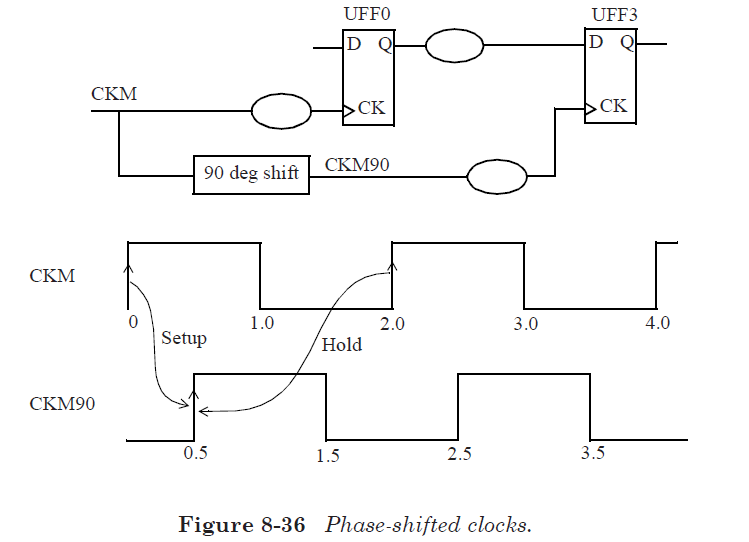

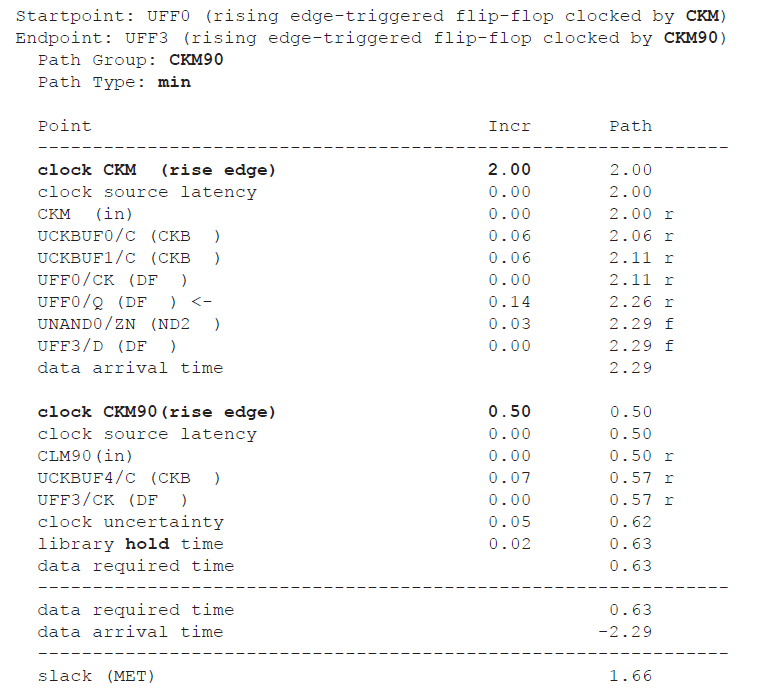

3、相移

时钟 90 度相移的例子:

create_clock -period 2.0 -waveform {0 1.0} [get_ports CKM]

create_clock -period 2.0 -waveform {0.5 1.5}

[get_ports CKM90]

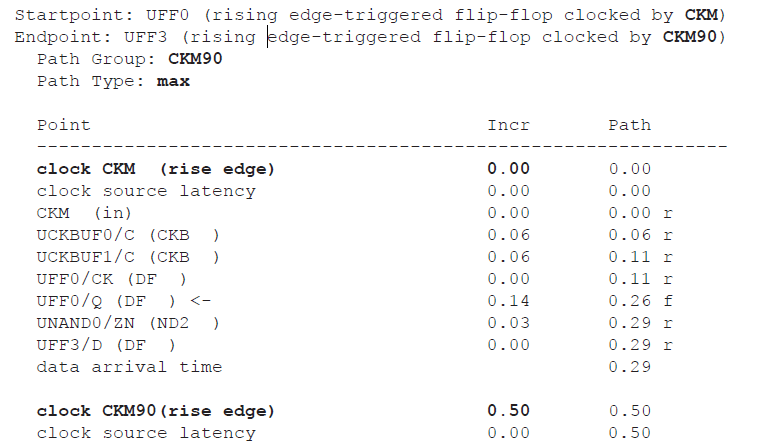

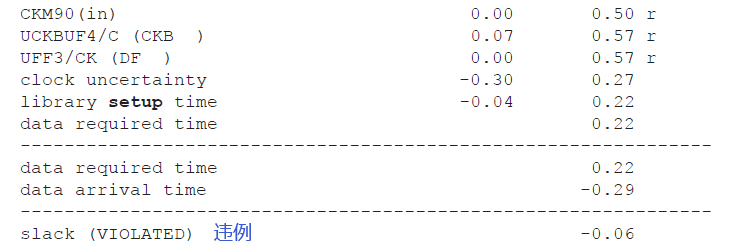

建立时间:

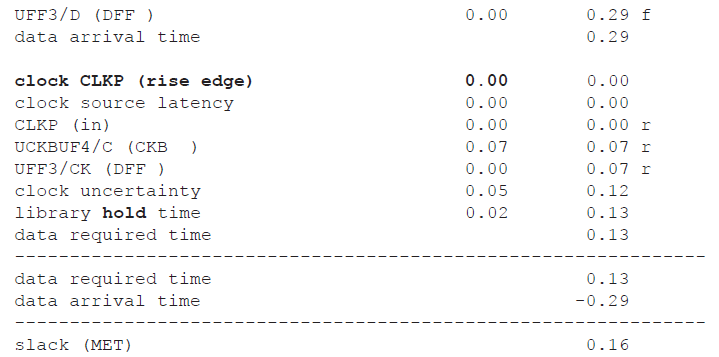

保持:

参考说明

【1】B站 邸老师学习视频。

【2】Static Timing Analysis for Nanometer Designs A Practical Approach . J. Bhasker • Rakesh Chadha

最后

以上就是笨笨小海豚最近收集整理的关于静态时序分析(STA)——跨时钟域时序、多时钟1、跨时钟域时序2、多时钟参考说明的全部内容,更多相关静态时序分析(STA)——跨时钟域时序、多时钟1、跨时钟域时序2、多时钟参考说明内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复