减少Cache命中时间

概述

重要性

- 命中时间直接影响到处理器的时钟频率。

- 在当今的许多计算机中,往往是Cache的访问时间限制了处理器的时钟频率。

五种策略

优化策略一:使用容量小、结构简单的Cache

-

硬件越简单,速度就越快;

-

应使Cache足够小,以便可以与CPU一起放在同一块芯片上。

-

把Cache的标识放在片内,而把Cache的数据存储器放在片外。

优化策略二:虚拟Cache

-

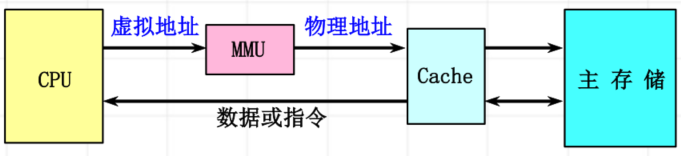

物理Cache

-

使用物理地址进行访问的传统Cache。

-

标识存储器中存放的是物理地址,进行地址检测也是用物理地址。

-

缺点:

- 地址转换和访问Cache串行进行,访问速度很慢。

-

-

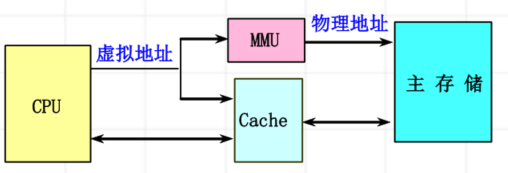

虚拟Cache

-

可以直接用虚拟地址进行访问的Cache。标识存储器中存放的是虚拟地址,进行地址检测用的也是虚拟地址。

-

优点:

- 在命中时不需要地址转换,省去了地址转换的时间。、

- 即使不命中,地址转换和访问Cache也是并行进行的,其速度比物理Cache快很多。

-

并非都采用虚拟Cache

-

虚拟Cache的清空问题(虚拟地址是跟进程相关的)

- 解决方法:在地址标识中增加PID字段(进程标识符)

- 三种情况下不命中率的比较:

- 单进程,PIDs,清空

- PIDs与单进程相比:+0.3%~+0.6%

- PIDs与清空相比:—0.6%~—4.3%

-

同义和别名:对同一物理地址采用多种不同形式的虚拟地址。

-

-

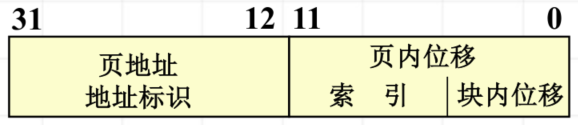

优化策略三:虚拟索引+物理标识

-

用虚地址中页内位移作为Cache的索引,标识用物理地址;

-

优点:

- 兼得虚拟Cache和物理Cache的好处

-

局限性

- Cache容量受到限制 (页内位移)

- Cache容量 ≤ 页大小×相联度

-

举例:IBM3033的Cache

- 页大小=4KB,相联度=16

- Cache容量=16×4KB=64KB

优化策略四:Cache访问流水化

- 对第一级Cache的访问按流水方式组织

- 访问Cache需要多个时钟周期才可以完成

- Pentium访问指令Cache需要一个时钟周期

- Pentium Pro到PentiumⅢ需要两个时钟周期

- Pentium 4则需要4个时钟周期

- 不能够真正减少Cache命中时间,但是可以提高时钟频率,提高Cache的带宽。

优化策略五:踪迹Cache

- 开发指令级并行性所遇到的一个挑战是:

- 当要每个时钟周期流出超过4条指令时,要提供足够多条彼此互不相关的指令是很困难的。

- 一个解决方法:采用踪迹Cache

- 存放CPU所执行的动态指令序列包含了由分支预测展开的指令,该分支预测是否正确需要在取到该指令时进行确认。

- 优缺点

- 地址映象机制复杂

- 相同的指令序列有可能被当作条件分支的不同选择而重复存放

- 能够提高指令Cache的空间利用率。

最后

以上就是坚强水池最近收集整理的关于【体系结构系列】减少Cache命中时间的全部内容,更多相关【体系结构系列】减少Cache命中时间内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[计算机体系结构] Cache 基本概念](https://www.shuijiaxian.com/files_image/reation/bcimg21.png)

发表评论 取消回复